delay flipflop

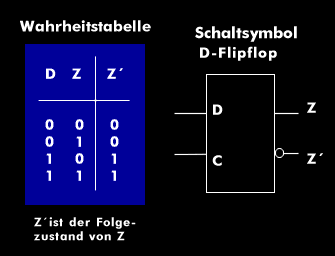

The D flipflop is a clocked flipflop with an information input "D" and a clock input "C". The "D" stands for delay and means a delayed transfer of the input data to the output.

The D flip-flop is switched exclusively by the edge of the clock pulse, independent of an intermediate change of state at the information input. The clock input is switched on the rising as well as on the falling edge of the clock pulse and transfers the level at the information input to the output with a delay. The outputs Z and Z'are state inverted. If the input D and the clock signal C are Lo, both outputs are Lo. With the rising edge of the clock signal, the changeover from Lo to Hi state and vice versa takes place.

The D flip-flop is used in electronic memories because the output remains constant unless it is intentionally changed by changing the state of the D input followed by a rising clock signal.

The D flip-flop are used in shift registers. For example, by cascading eight D flip-flops in sequence, one byte (8 bits) of information can be stored after 8 clock cycles.