rapid input output (RapidIO)

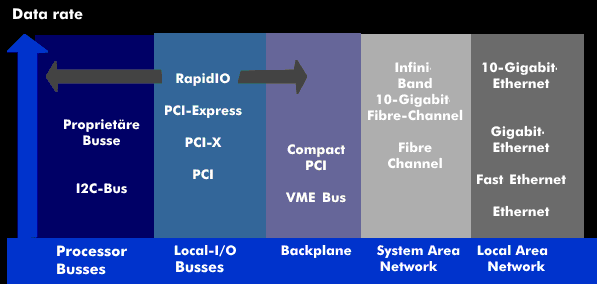

The RapidIO standard defines a serial interface for chip-to-chip connections up to system- level connections via the backplane. The high- performance, packet-oriented bus technology was developed for embedded systems and is especially suitable for network and communication systems, as well as for enterprise storage.

The RapidIO Trade Association, which includes well-known companies from the communications, networking, chip and embedded systems industries, developed the RapidIO bus and promotes it as an open standard. The RapidIO bus is designed to eliminate the bottleneck with which components in network and communication devices and systems communicate with each other.

Data rate and fault tolerance

The RapidIO bus is characterized by a high data rate, fault tolerance and low latency. Thanks to its software transparency, no special device drivers are required. The specifications of the RapidIO bus describe a high-performance interconnect architecture with which data and control signals can be transferred between microprocessors, digital signal processing units, communication and network processors, memory units and peripheral devices. At the physical level, chip-to-chip and board-to-board transfers are possible with data throughput exceeding 10 Gbps over standard printed circuit boards. In addition, the Rapid IO bus can serve as a bridge to other bus systems such as the PCI bus, PCI-X and Infiniband.

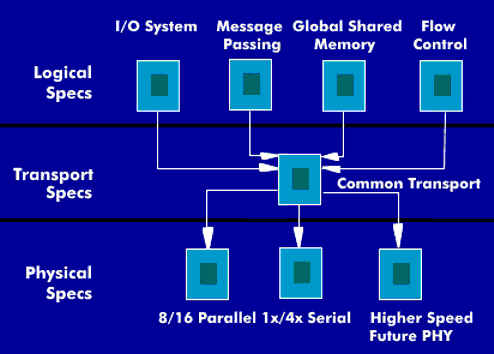

The RapidIO standard is a packet-switched connection architecture, but the concept is aimed at communication between processors and peripheral units. The RapidIO architecture is divided into three layers for logical connections, data transport and physical specifications. To meet the different requirements for the connections between devices and boards, a serial and a parallel connection have been specified for the physical layer. Parallel RapidIO uses Low Voltage Differential Signaling( LVDS) with clock frequencies from 250 MHz to 1 GHz, with 8-bit or 16-bit transmission. This results in a data throughput of 2 GB/s for the 16-bit variant at a clock frequency of 1 GHz. The serial variant, Serial RapidIO( SRIO), uses 10 Gigabit Ethernet with the XAUI interface and 8B/10B coding.

The original concept of the RapidIO bus had a data rate of 10 Gbit/s and used 8-bit wide input and output ports. With LVDS it is possible to scale the number of ports to 16 bit wide ports or higher and thus achieve a multiple of the data rate.