boundary scan test (BST)

Boundary scan technology (BScan), also known as boundary scan test (BST), was standardized in 1990 under IEEE 1149.1. Boundary-scan can be used to perform electrical tests and on- board programming of assembled printed circuit boards.

In contrast to the in-circuit test, physical access to the boundary scan does not take place via many test probes, but only via four connection lines. A major advantage of this test technique is that boards can be tested without having physical access to the often hidden connections.

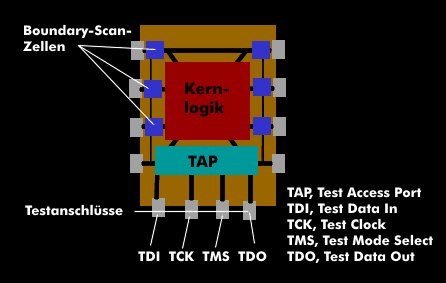

In addition to the core logic, boundary-scan-enabled chips have an additional logic, the boundary-scan cell, with a test access port( TAP). The boundary-scan cells are integrated between the core logic and the physical pins of the circuit. Data streams travel to and from the boundary cell via the test access port. These signals can be tapped at pins of other chips, for example, to test solder connections and traces.

Semiconductor manufacturers offer components with a corresponding boundary-scan port as standard. These are usually referred to as Joint Test Action Group( JTAG) after the standardization body. In boundary-scan, the scannable devices form test clusters and test networks within the board, which is connected to the test system via four lines.

Creating the test software takes only a few days, especially since it is possible to test the assemblies individually throughout the development phase of a board and reuse this test data later during prototype and production testing. Boundary-scan detects the same defects as the other test methods. These include defective electrical components, press-fit defects, solder defects, and placement and solder bath defects in SMT and through-holetechnology( THR).

The JTAG standards IEEE 1149.1 define the specifications of the TAP bus as well as the scan cells:

IEEE 1149.1: Static digital link test.

IEEE 1149.4: Analog component test and analog connection and parameter test.

IEEE 1149.6: Dynamic, digital connection test, for example for Low Voltage Differential Signaling( LVDS) and PCI Express.

IEEE 1532: Standard for in-system programming of Complex Programmable Logic Devices( CPLD) and Field Programmable Gate Arrays( FPGA).