Power5 ist ein von IBM entwickelter und im Herbst 2003 vorgestellter Doppelkernprozessor, bei dem jeder der beiden Prozessoren 2-Wege- Multithreading unterstützt und damit 4 logische Prozessoren bildet. Der ca. 400 qmm große Power5- Chip besteht aus 276 Millionen Transistoren und ist in 130-nm-Technologie ausgeführt. Er hat eine Taktfrequenz von 2 GHz.

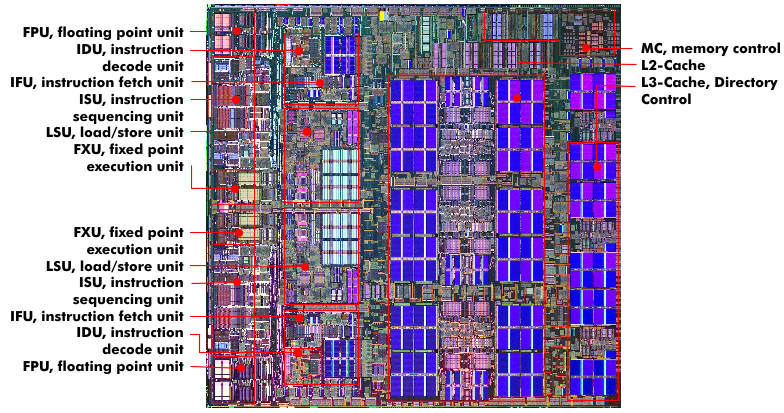

Jeder Prozessorkern hat 120 Namensregister für die Berechnung von Ganzzahlen und Fließkommazahlen sowie acht Ausführungseinheiten. Sie arbeiten mit bis zu 5 Anweisungen pro Taktzyklus und haben eine Rechenleistung von 4 FLOPS pro Taktzyklus. Die beiden Prozessoren teilen sich ein ultraschnelles Level-2-Cache mit einer Speicherkapazität von 1,92 Megabyte ( MB), das einen Datendurchsatz von ca. 200 GB/s hat. Das Level-3-Cache arbeitet mit der halben Taktfrequenz der Zentraleinheit, also mit 1 GHz, und ist 36 MB groß.

Power5 hat eine Busbreite von 256 Bit, die in zwei unidirektionale Busse geteilt werden können. Die Taktrate für den Bus liegt um die 2 GHz. Zur Leistungssteigerung arbeitet Power5 mit Simultaneous Multithreading ( SMT).

Eingesetzt wird der Power5, der Virtualisierung unterstützt, in Servern der iSeries und pSeries sowie in Blade-Servern.