Die Boundary-Scan-Technologie (BScan), auch als Boundary Scan Test (BST) bezeichnet, wurde 1990 unter IEEE 1149.1 standardisiert. Mit dem Boundary-Scan können elektrische Tests und On-Board-Programmierungen von bestückten Leiterplatten durchgeführt werden.

Im Gegensatz zum In-Circuit-Test erfolgt beim Boundary-Scan der physikalische Zugriff nicht über viele Testspitzen, sondern lediglich über vier Verbindungsleitungen. Ein wesentlicher Vorteil dieser Testtechnik besteht darin, dass man Baugruppen testen kann, ohne physikalischen Zugriff auf die oft verdeckten Anschlüsse zu haben.

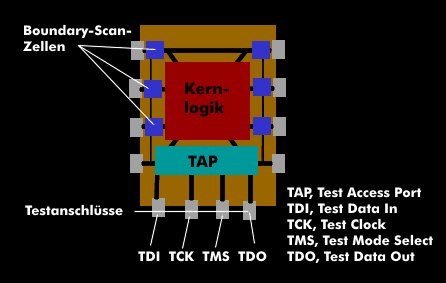

Boundary-Scan-fähige Chips haben neben der Kernlogik eine zusätzliche Logik, die Boundary-Scan- Zelle, mit einem Test Access Port ( TAP). Die Boundary-Scan- Zellen sind dabei zwischen Kernlogik und den physikalischen Pins des Schaltkreises integriert. Über den Test Access Port gelangen die Datenströme von und nach der Boundary-Zelle. Diese Signale können beispielsweise zum Testen von Lötverbindungen und Leiterbahnen an Pins von anderen Chips abgegriffen werden.

Die Halbleiterhersteller bieten standardmäßig Bauelemente mit einem entsprechenden Boundary-Scan- Anschluss an. Diese werden in der Regel nach dem Standardisierungsgremium mit Joint Test Action Group ( JTAG) bezeichnet. Beim Boundary-Scan bilden die scanfähigen Bauelemente Test- Cluster und Test- Netzwerke innerhalb der Baugruppe, die über vier Leitungen mit dem Testsystem verbunden ist.

Die Erstellung der Testsoftware nimmt nur einige Tage in Anspruch, zumal man während der gesamten Entwicklungsphase einer Platine die Baugruppen auch einzeln testen kann und diese Testdaten später beim Prototypen- und beim Fabrikationstest wieder verwenden kann. Boundary-Scan erkennt die gleichen Fehler wie die anderen Testverfahren. Dazu gehören fehlerhafte elektrische Bauelemente, Einpressfehler, Lötfehler sowie Bestückungsfehler und Lotbadfehler bei der SMT-Technik und Durchstecktechnik ( THR).

Die JTAG-Standards IEEE 1149.1 legen die Spezifikationen des TAP-Busses sowie der Scan-Zellen fest:

IEEE 1149.1: Statischer, digitaler Verbindungstest.

IEEE 1149.4: Test analoger Bauteile und analoger Verbindungs- und Parametertest.

IEEE 1149.6: Dynamischer, digitaler Verbindungstest, beispielweise für Low Voltage Differential Signalling ( LVDS) und PCI-Express.

IEEE 1532: Standard zur In- System-Programmierung von Complex Programmable Logic Devices ( CPLD) und Field Programmable Gate Arrays ( FPGA).