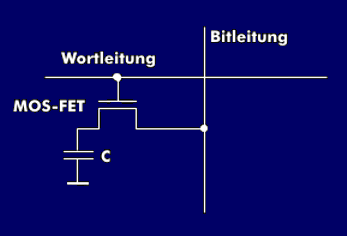

Die in Dynamic RAMs (DRAM) benutzte Bitzelle oder Speicherzelle speichert den Bitwert als Kleinstladung in einer Kapazität. Bei diesem Prinzip fungiert ein MOSFET, ein Transistor in MOS-Technologie, als Schalter und gleichzeitig als Kapazität.

Die Kapazität wird aus der Kapazität der Drainzone und dem Substrat gebildet und liegt im Bereich von wenigen Femto- Farad (fF), was einem Präfix von `10^-15` entspricht.

In dieser Kleinstkapazität werden die beiden möglichen digitalen Zustände gespeichert und über die Bit- und Wortleitung ein- bzw. ausgelesen. Beim Speichern überschreibt die Wortleitung den Ladungszustand, beim Auslesen dient die Kapazität als Treiber für die Bitleitung. Da die Ladung in der Bitzelle ständig abfließt, werden die Ladungszustände durch ein regelmäßiges Refresh aufrecht erhalten.